半导体产业纵横RISC-V为设计新处理器提供了一定程度的灵活性,因为指令集不是在 ISA 级别定义的,而是通过处理器和其他设计参数进行编译。

RISC-V被描述为基于精简指令集计算机(RISC) 原则的开放标准指令集架构 (ISA)。归结起来,RISC 简化了需要处理器完成任务的指令集。但是,与大多数 ISA 不同的是,RISC-V 是在开源许可下提供的,这意味着任何人都可以为其开发做出贡献,并且不需要付费使用。

每个处理器都使用 ISA 来按照一组规定的参数运行,并且几乎所有这些参数都是专有的。虽然有些是可授权的,但很少有免费的,这使得RISC-V 的独特之处在于任何人都可以使用指令集来开发自己的处理器。

该指令集于 2010 年在伯克利开发,具有多种优势,包括其开放性、简单性、全新设计、模块化、可扩展性和稳定性——与已有数十年历史且无法处理最新计算工作负载的传统 ISA 不同。这个想法是为了消除设计处理器内核的复杂性,它已经演变成一个软件可见的界面,用于无数的实现,包括嵌入式系统和超级计算机等。

RISC-V的核心是对处理器设计应如何运行的描述,本质上是对软件如何与处理器通信的描述性基础。RISC-V为设计新处理器提供了一定程度的灵活性。这是因为指令集不是在 ISA 级别定义的,而是处理器和其他设计参数的编译。因此,工程师和制造商可以快速实现最小指令集以及定义明确的自定义扩展,以设计用于下一代工作负载的处理器。

RISC-V还利用已建立和通用的 IP 构建块来开发创客社区不断增长的共享工具和开发资源集。来自用户群的贡献降低了与研发相关的成本并加快了上市时间,从而提高了设备的整体效率。

01

模块化设计、基础和扩展

RISC-V指令集在设计上是模块化的,这意味着用户可以自定义平台并放入他们需要的任何扩展。ISA 基础及其扩展是在行业、研究人员和教育机构之间共同开发的。

分解后,ISA 内核提供指定的指令(和编码)、控制流、寄存器、内存和寻址逻辑操作以及辅助设备。单独使用RISC-V 可以实现具有完整软件支持的简化通用计算机,包括通用编译器。

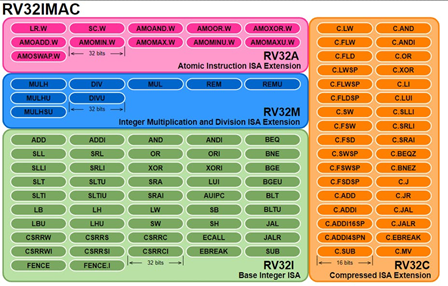

到目前为止,四个基本 ISA 的特征在于整数寄存器的宽度和相应的地址大小以及整数寄存器的数量。两个主要的基础 ISA 对应于 32 位和 64 位地址空间,分别是 RV32I 和 RV64I。此外,子集变体 RV32E 配备了一半的整数寄存器,专为小型微控制器而设计。

所有基本 ISA 都具有可用于特定用例的差异化功能。但是,它们被分开以优化每个而不需要支持其他的操作。

为了更好地理解可能实现的功能组合,设计了一个广泛的参考来定义和指定每一个,这些在当前批准的非特权 ISA 规范的第 27 章中进行了概述。首先指定指令集基础,然后是 RISC-V、寄存器位宽和变体的编码。

指定实现扩展的字母出现在集合基数之后。每个字母后面可以跟一个主要字母,可以选择后面跟“p”和一个次要选项编号。如果未使用次要版本号,则默认为 0,如果不存在所有版本号,则默认为 1.0。

为了便于阅读,扩展名之间可以使用下划线,例如,RV32I2_M2_A2。当添加多个扩展时,术语变得更加广泛。

一旦确定了基础,用户就可以添加这些扩展来定义核心的确切规则。目前开放和批准的扩展包括:

M:整数乘法和除法的标准扩展

A:原子指令的标准扩展

F:单精度浮点的标准扩展

D:双精度浮点的标准扩展

G:基本及以上扩展的简写

Q:四精度浮点的标准扩展

L:十进制浮点的标准扩展

C:压缩指令的标准扩展

B:位操作的标准扩展

J:动态翻译语言(C#、Java、Haskell 等)的标准扩展

T:事务内存的标准扩展

P:打包 SIMD 指令的标准扩展

V:向量运算的标准扩展

K:标量密码学的标准扩展

N:用户级中断的标准扩展

H:管理程序的标准扩展

S:主管级指令的标准扩展

现在我们对扩展有了一个概述,让我们看一个实践示例并解码带有 RV32IMAC (见图)内核的 GD32V 是如何分解的:GD32V 是具有整数乘法和除法的 32 位 RISC-V 内核 (RV32I) (M)、原子指令 (A) 和压缩(16 位)指令 (C)。

来源:Eduardo Corpeno

另一个例子是 Kendryte 的K210双核 RISC-V RV64IMAFDC/RV64GC SoC(片上系统)。分解后,它转换为 64 位 RISC-V 处理器 (RV64I),具有整数乘除法 (M)、原子指令 (A)、单精度 (F) 和双精度 (D) 浮点(I + M + A + F + D = G),以及压缩指令 (C)。

尽管列表已经很广泛,但当没有合适的现成 ISA 扩展适合设计需求时,可能会出现这种情况。在这些情况下,RISC-V 规范允许添加自定义 ISA 扩展。这可以是工程师或制造商的特定集成和关键差异化因素。

由于 RISC-V 生态系统的独特性,自定义 ISA 扩展不会违反主要规范。即使有额外的指令,处理器仍然完全符合 RISC-V 标准,并且可以运行从生态系统中获得的通用软件堆栈。

02

应用与未来发展许多公司正在利用 RISC-V 创建定制处理器,旨在满足新技术的功率和性能要求,包括人工智能 (AI)、物联网 (IoT) 以及虚拟和增强现实 (VR/AR)。RISC-V 还被用于针对从边缘计算到云服务器和高性能计算 (HPC) 的应用程序的定制处理器。此外,公司正在慢慢推出 RISC-V 通用处理器,用于笔记本电脑、台式机和数据中心,并具有垂直和水平扩展能力。

SiFive是一家致力于生产 RISC-V 硬件的公司,已经生产了多款旨在处理最大吞吐量和广泛工作负载的处理器。这些范围从配备 256 位矢量引擎的 8 级、双问题、有序架构到高级无序处理器,包括 P650、P550 和 P270。这些产品旨在与许多移动设备和开发板中的 Arm Cortex 生态系统直接竞争。

包括Western Digital和Seagate在内的硬盘驱动器公司正在其下一代存储解决方案中实施 RISC-V,用于以数据为中心和对安全至关重要的应用程序。

据RISC-V 国际基金会称,2010 年约有 600 名成员签约推出支持 RISC-V 的硬件,而在过去十年中,这一数字已激增至 2,400 多个。他们还预计,到 2025 年,RISC-V 将在整个 CPU 范围内采用,包括企业和消费市场。

许多公司和学术机构目前正在开发基于 RISC-V 的处理器,预计将在未来几年发布,包括 ATSC、Cambridge、Esperanto Technologies、ETH Zurich、NVIDIA 等。虽然当前的 RISC-V 技术目前无法与 AMD 和 Intel 的 x86 产品竞争,但开源指令集架构有足够的动力在不久的将来生产具有竞争力的硬件。(来源:半导体产业纵横)